## Quad Universal Asynchronous Receiver/Transmitter (UART) with 64-BYTE FIFO & Infrared Encoder/ Decoder

### Description

The IMP16C654 is a universal asynchronous receiver and transmitter (UART) and is *available in different packages. The IMP16C654 is an quad UART with enhanced features* like 64 byte deep transmit and receive fifo's, programmable transmit and receive trigger levels to enable data rates of 1.5Mbps with low system interface overhead and in band/out of band flow controls. Status registers provide the user with error indications and operational status, modem interface control status. Interrupt levels are software programmable to suit different system requirements. Internal loopback capability facilitates diagnostics. Low power modes of IMP16C654 enables its use in critical low power applications.

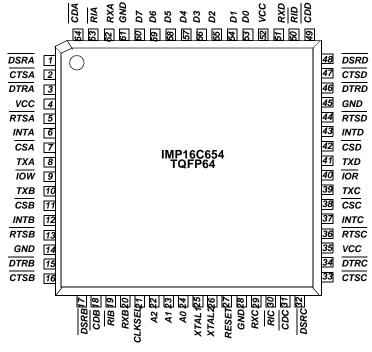

The IMP16C654 is available in industry standard 64 pin TQFP, 68 pin PLCC and 100 pin QFP packages. Each additional pin on the package makes available additional range of features for the application.

### **Key Features**

- Compatibility with the Industry Standard ST16C454, ST68C454, ST68C554, TL16C554, TL16C554 and TL16C754.

- Data Rates upto 1.5Mbps.

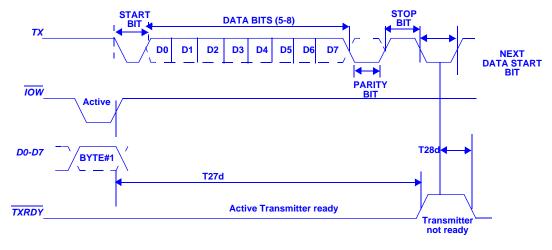

- 64 byte transmit FIFO and receive fifo.

- Four selectable trigger level based FIFO interrupt Generation.

- CTS/RTS flow control.

- Xon/Xoff flow control.

- Selectable clock frequency pre-scaler and programmable baud rate generator.

- IrDA v1.0 encoder/decoder interface along with standard wired modem interface.

- Low power mode.

- 3.3V operation.

## **Pin Description**

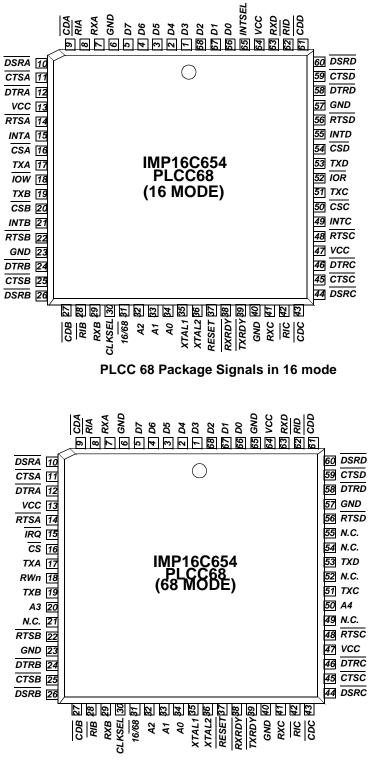

**TQFP64 Package Signals**

PLCC 68 Package Signals in 68 mode

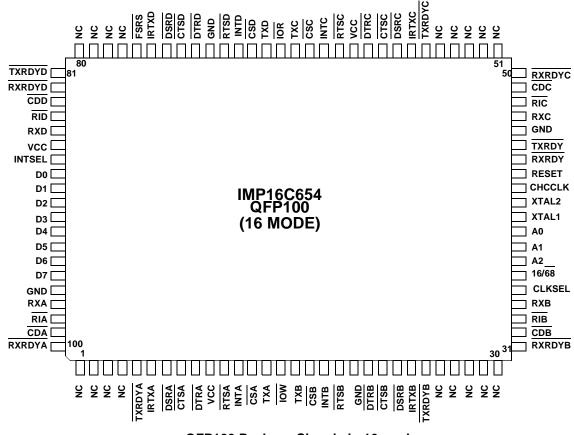

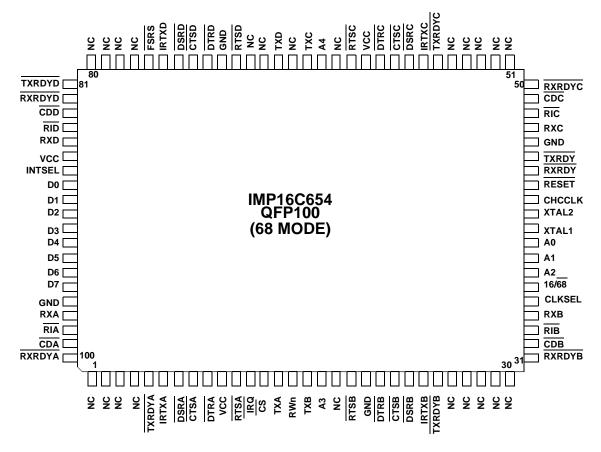

QFP100 Package Signals in 16 mode

QFP100 Package Signals in 68 mode

## **Data Communications**

#### Table 1 : Signal Description

| Pin              |                | Pin             |                                  |      | Pin Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |

|------------------|----------------|-----------------|----------------------------------|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Gymbol           | PLCC68         | TQFP64          | QFP100                           | Туре |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |

| NC               | -              | -               | 1-4<br>26-30,<br>51-55,<br>77-80 | -    | No Connect.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |

| GND              | 6,23,<br>40,57 | 14,28,<br>45,61 | 20,46,<br>71,96                  |      | Ground.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |

| VCC              | 13,47<br>64    | 4,<br>35,52     | 10,61<br>86                      |      | Power                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |

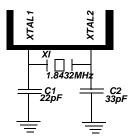

| XTAL1            | 35             | 25              | 40                               | I    | Crystal or External Clock Input - Functions as a crystal input or as an external clock input. A crystal can be connected between this pin and XTAL2 to form an internal oscillator circuit. Alternatively, an external clock can be connected to this pin to provide custom data rates.                                                                                                                                                                                                                                                      |  |

| XTAL2            | 36             | 26              | 41                               | 0    | Output of the Crystal Oscillator or Buffered Clock - Crystal oscillator output or buffered clock output. When external clock is connected to XTAL1, this pin should be left floating.                                                                                                                                                                                                                                                                                                                                                        |  |

| RESET/RESET      | 37             | 27              | 43                               | I    | Reset In the intel processor interface mode, this is active high reset<br>for the IMP16C654. In motorola interface mode, this is active low<br>reset for the IMP16C654.                                                                                                                                                                                                                                                                                                                                                                      |  |

| CLKSEL           | 30             | 21              | 35                               | I    | Clock Select (input with internal pullup) - This pin selects the clock pre-scaler. If connected to logic 1, the input clock is selected. If connected to logic 0, divide by 4 clock is selected. MCR bit 7 can override this state following reset or initialization.                                                                                                                                                                                                                                                                        |  |

| CPU Interface Si | gnals          | •               |                                  |      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |

| 16/68            | 31             | -               | 36                               | I    | 16/68 Interface Type Select (input with internal pull-up). This input selects CPU interface to be 16 (Intel) or 68 (Motorola) bus interface. The functions of $\overline{IOR}$ , $\overline{IOW}$ , INT A-D, and $\overline{CS}$ A-D are re-assigned with the logical state of this pin. When this pin is a logic 1, the intel type CPU bus interface is selected. When this pin is a logic 0, the motorola type CPU bus interface is selected. This pin is not available on 64 pin packages which allows only intel type CPU bus interface. |  |

| A0,A1,A2         | 34,33,32       | 24,23,22        | 39,38,37                         | I    | Address-0-2 Inputs are used to select a specific internal register of one of the four UARTs for read/write access.                                                                                                                                                                                                                                                                                                                                                                                                                           |  |

| CSA/CS           | 16             | 7               | 13                               | I    | Chip Select. (active low) - In the motorola bus interface mode, this pin functions <u>as</u> a chip enable. In this case, all four UARTs are enabled when the CS pin is a logic 0. An individual UART channel is selected by the address bits A3-A4.<br>When the intel bus interface mode is selected, this pin functions as CSA, selecting UART channel A registers for read/write accesses.                                                                                                                                                |  |

| CSB/A3           | 20             | 11              | 17                               | I    | Chip Select (active low) - In motorola bus interface mode, this pin<br>provides one of the two additional address lines required to select<br>one of the 4 UARTs in the IMP16C654.<br>In Intel bus interface mode, this active low input selects UART chan-<br>nel B registers for read/write accesses.                                                                                                                                                                                                                                      |  |

## **Data Communications**

#### Table 1 : Signal Description

| Symbol              | Pin      |          | Pin Description |                                                                                                                                                                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|---------------------|----------|----------|-----------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Symbol              | PLCC68   | TQFP64   | QFP100          | Туре                                                                                                                                                                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| CSC/A4              | 50       | 38       | 64              | I                                                                                                                                                                                               | Chip Select (active low) - In motorola bus interface mode, this pin<br>provides one of the two additional address lines required to select<br>one of the 4 UARTs in the IMP16C654.<br>In Intel bus interface mode, this active low input selects UART chan-<br>nel C registers for read/write accesses.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| CSD                 | 54       | 42       | 68              | I Chip Select (active low) - In motorola bus interface mode, th<br>NC(No Connect).<br>In Intel bus interface mode, this active low input selects UA<br>nel D registers for read/write accesses. |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| D0-D7               | 66-5     | 53-60    | 88-95           | I/O                                                                                                                                                                                             | Data Bus (Bi-directional) - These are the eight bit, bidirectional data bus for transferring information to or from the controlling application.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| INTSEL              | 65       | -        | 87              | I                                                                                                                                                                                               | Interrupt Select. (active high, with internal pull-down) - When the intel<br>bus interface mode is selected, this pin can be used in conjunction<br>with MCR bit-3 to enable or disable the tri-stating of the interrupt out-<br>puts for each of the channels. Interrupt outputs are enabled continu-<br>ously by connecting this pin to a logic 1.<br>Connecting this pin to a logic 0 allows MCR bit-3 to control the three<br>state interrupt output. In this mode, MCR bit-3 is set to a logic 0 to<br>enable the three state outputs.<br>This pin must be connected to logic 0 in motorola bus interface mode.<br>Since this pin is not available in TQFP64 package, two different ver-<br>sions are available. In IMP16C654D, interrupt operates in continuous<br>interrupt mode and this input is bonded to logic1, while the<br>IMP16C654 the interrupt pin function is controlled by MCR bit 3 and<br>the INTSEL input is bonded to ground. |

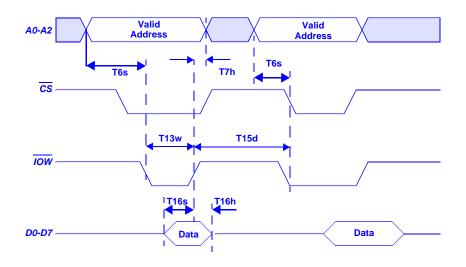

| ĪŌR                 | 52       | 40       | 66              | I                                                                                                                                                                                               | Read strobe. (active low Strobe) - This function is associated with the intel bus interface mode only. A logic 0 transition on this pin will load the contents of an Internal register defined by address bits A0-A2 onto the data bus (D0-D7) for access by an application. This pin is NC in motorola bus interface mode.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

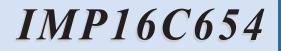

| IOW/RWn             | 18       | 9        | 15              | I                                                                                                                                                                                               | Write strobe. (active low strobe) - In intel bus interface mode, a logic 0 transition on this pin will transfer the contents of the data bus (D0-D7) from the application to an internal register that is selected. In motorola bus interface mode, this pin acts as active high read strobe or active low write strobe.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| INTA/ĪRQ            | 15       | 6        | 12              | 0                                                                                                                                                                                               | Interrupt A/ $\overline{IRQ}$ - In Intel bus interface mode, this pin is active high<br>and goes active if any one of the enabled causes of interrupts in the<br>channel A UART is requiring application attention. Its going high is<br>also controlled by INTSEL and MCR bit 3.<br>In motorola bus interface mode, this pin is active low and goes active<br>if any one of the enabled causes of interrupts in any of the 4 UART<br>channels is requiring applications attention. INTSEL must be<br>grounded for this pin to work properly in motorola bus interface mode.                                                                                                                                                                                                                                                                                                                                                                          |

| INTB,<br>INTC, INTD | 21,49,55 | 12,37,43 | 18,63,69        | 0                                                                                                                                                                                               | Interrupt B, C, D (active high) - This function is associated with the intel bus interface mode only. These pins provide individual channel interrupts, INT B-D. INT B-D are enabled when MCR bit-3 is set to a logic 1, interrupts are enabled in the interrupt enable register (IER), and when an interrupt condition exists. In motorola bus interface mode, these pins are NC's.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

## **Data Communications**

### Table 1 : Signal Description

| Symbol                                   | Pin Symbol Turce |                 | Pin Description   |      |                                                                                                                                                                                                                                                                                                                                                                                                 |  |

|------------------------------------------|------------------|-----------------|-------------------|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Gymbol                                   | PLCC68           | TQFP64          | QFP100            | Туре |                                                                                                                                                                                                                                                                                                                                                                                                 |  |

| FSRS                                     | -                | -               | 76                | I    | Active low FIFO Status Register Select (internal pull-up) - When loselects the FIFO status register for read. The address and the signals are not used when this signal is active low.                                                                                                                                                                                                          |  |

| RXRDY                                    | 38               | -               | 44                | 0    | Receive Ready (active low) - This function is associated with 68/100<br>pin packages only. RXRDY when low indicates that at least one<br>channel receive FIFO contains received data. This pin goes to a logic<br>1 when the FIFO/RHR is empty. For 64/68 pin packages, individual<br>channel RX status is read by examining individual internal registers<br>using CS and A0-A4 pin functions. |  |

| TXRDY                                    | 39               | -               | 45                | 0    | Transmit Ready (active low) - This function is associated with 68/100<br>pin package only. TXRDY when 0 indicates a buffer ready status, i.e.,<br>at least one location is empty and available in one of the TX channels<br>(A-D). This pin goes to a logic 1 when all four channels have no more<br>empty locations in the TX FIFO or THR.                                                     |  |

| RXRDYA,<br>RXRDYB,<br>RXRDYC,<br>RXRDYD  | -                | -               | 100, 31,<br>50,82 | 0    | Receive Ready (active low) - These pins are available on QFP100 package only. When low, indicates at least one byte available in receive FIFO for the application to read. Signal goes high when there are no bytes in the receive fifo or the number of bytes in the receive fifo falls below the programmed trigger level.                                                                    |  |

| TXRDYA,<br>TXRDYB,<br>TXRDYC,<br>TXRDYD  | -                | -               | 5, 25,<br>56, 81  | 0    | Transmit Ready (active low) - These pins are available on QPF100 package only. When low when FIFO is empty in DMA mode and FIFO is below trigger level in DMA mode.                                                                                                                                                                                                                             |  |

| CHCCLK                                   | -                | -               | 42                | I    | Channel C Clock - This pin is available on QFP100 package only.<br>This pin provides the clock for UART channel C. An external clock or<br>XTAL2 must be connected to this pin for normal operation.                                                                                                                                                                                            |  |

| Serial Interface S                       | Signals          |                 |                   | •    |                                                                                                                                                                                                                                                                                                                                                                                                 |  |

| CDA, CDB,<br>CDC, CDD                    | 9,27,<br>43,61   | 64,18,<br>31,49 | 99,32,<br>49,83   | I    | Carrier Detect (active low) - These inputs are associated with individ-<br>ual UART channels A through D. A logic 0 on this pin indicates that a<br>carrier has been detected by the modem for that channel.                                                                                                                                                                                    |  |

| <u>CTSA</u> , <u>CTSB,</u><br>CTSC, CTSD | 11,25<br>45,59   | 2,16<br>33,47   | 8,22,<br>59,73    | I    | Clear to Send (active low) - These inputs are associated with individ-<br>ual UART channels, A through D. A logic 0 on the CTS pin indicates<br>the modem or data set is ready to accept transmit data from the<br>554D. Status can be tested by reading MSR bit-4.                                                                                                                             |  |

| DSRA, DSRB,<br>DSRC, DSRD                | 10,26<br>44,60   | 1,17<br>32,48   | 7,23,<br>58,74    | I    | Data Set Ready (active low) - These inputs are associated with indi-<br>vidual UART channels, A through D. A logic 0 on this pin indicates<br>the modem or data set is powered-on and is ready for data exchange<br>with the UART. This pin has no effect on the UARTs transmit or<br>receive operation.                                                                                        |  |

| <u>RIA,</u> <u>RIB,</u><br>RIC, RID      | 8,28<br>42,62    | 63,19<br>30,50  | 98, 33,<br>48,84  | I    | Ring Indicator (active low) - These inputs are associated with individ-<br>ual UART channels, A through D. A logic 0 on this pin indicates the<br>modem has received a ringing signal from the telephone line. A logic<br>1 transition on this input pin will generate an interrupt.                                                                                                            |  |

## **Data Communications**

Table 1 : Signal Description

| Symbol                                                   |                | Pin            |                                     |      | Pin Description                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|----------------------------------------------------------|----------------|----------------|-------------------------------------|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| eyev                                                     | PLCC68         | TQFP64         | QFP100                              | Туре |                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| DTRA, DTRB,<br>DTRC, DTRD                                | 12,24<br>46,58 | 3,15<br>34,46  | 9,21,<br>60,72                      | 0    | Data Terminal Ready (active low) - These inputs are associated with individual UART channels, A through D. A logic 0 on this pin indicates that the 554D is powered-on and ready. This pin can be controlled via the modem control register. Writing a logic 1 to MCR bit-0 will set the DTR output to logic 0, enabling the modem. This pin will be a logic 1 after writing a logic 0 to MCR bit-0. This pin has no effect on the UARTs transmit or receive operation. |

| <u>RTSA, RTSB,</u><br>RTSC, RTSD                         | 14,22<br>48,56 | 5,13<br>36, 44 | 11,19,<br>62,70                     | 0    | Request to Send (active low) - These outputs are associated with<br>individual UART channels, A through D. A logic 0 on the RTS pin indi-<br>cates the transmitter has data ready and waiting to send. Writing a<br>logic 1 in the modem control register (MCR bit-1) will set this pin to a<br>logic 0 indicating data is available. After a reset this pin will be set to a<br>logic 1. This pin has no effect on the UARTs transmit or receive oper-<br>ation.       |

| RXA, RXB,<br>RXC, RXD<br>(IRRXA, IRRXB,<br>IRRXC, IRRXD) | 7,29<br>41,63  | 62,20<br>29,51 | 97,34,<br>47,85                     | I    | Receive Data Input RX A-D These inputs are associated with indi-<br>vidual serial channel data input to the IMP16C654D. During the local<br>loopback mode, the RX input pin is disabled and TX data is internally<br>connected to the UART RX Input, internally. MCR bit 6 controls the<br>mode for this pin.                                                                                                                                                           |

| TXA, TXB,<br>TXC, TXD<br>(IRTXA, IRTXB,<br>IRTXC, IRTXD) | 17,19<br>51,53 | 8,10<br>39,41  | 14,16,<br>65,67<br>(6,24,<br>57,75) | 0    | Transmit Data - These outputs are associated with individual serial transmit channel data. During the local loopback mode, the TX input pin is disabled and TX data is internally connected to the UART RX Input. In QFP100 package, TX and IRTX both pins are available while in other packages the MCR bit 6 selects the mode.                                                                                                                                        |

## **General Description**

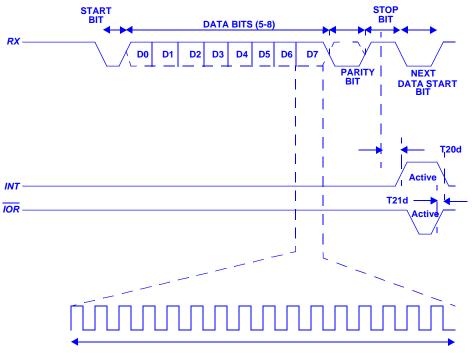

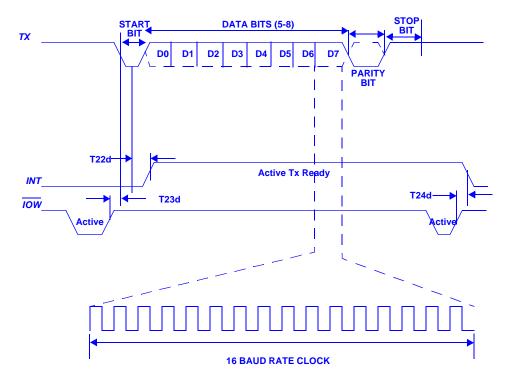

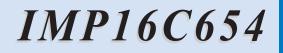

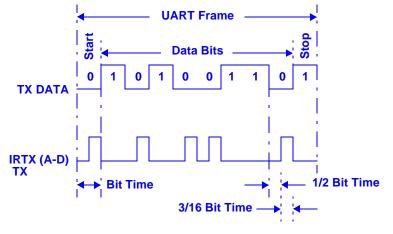

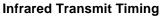

The IMP16C654 provides quad serial asynchronous transmit / receive functionality. It performs parallel to serial data conversion and frames each character according to programmed parameters. It also performs the serial to parallel data conversion after stripping of the framing bits from the characters. While framing the character, the transmitter adds start and stop bits and the parity bit for checking data integrity according to programmed parameters. The receiver strips the start and the stop bits and checks for character integrity by checking the parity bit if programmed.

The IMP16C654 provides easy interface to both motorola and intel processors. This is achieved by additional onboard logic that enables glueless interface to both intel and motorola processor busses. The IMP16C654 is capable of data transfers at 1.5 Mbps on each channel. It provides modem interface status/control inputs and outputs for easy of interface to modems. It provides independent baud rate generator for each channel.

The IMP16C654 is an upward solution that provides 64 bytes of transmit and receive FIFOs and can be software configured to work as 16C454/16C554. The 654 is designed to work in application environments that required high throughput. By providing deeper transmit and receive FIFO's and auto flow control features the IMP16C654 successfully allows increased latency in application servicing a request from the UARTs without loosing any data. Programmable trigger levels for transmit and receive fifo's provide additional option to fine tune the system to provide optimal performance.

The IMP16C654 also provides a pre-scaler which can select the input clock frequency to 1X or 4X depending on the state of CLKSEL input and the MCR bit 7. It also provides an external clock option which allows connection to a external MIDI oscillator for MIDI interface. The IMP16C654 also provide IrDA outputs for use in wireless applications. Loopback modes allow diagnostic of the hardware to locate faults quickly. In addition, the IMP16C654 provides low power mode to enable its use in low power UART applications.

The IMP16C654 is available if various packages and bonding options to allow multiple footprints to be supported in application environment. These footprints are compatible to industry standard parts offered by other vendors.

### **Functional Description**

#### The Intel Bus Interface Mode

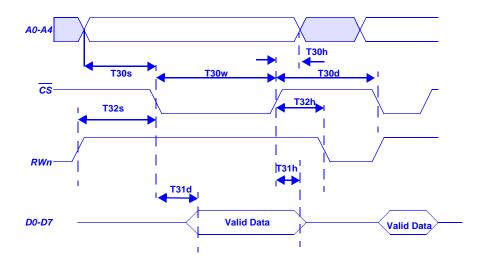

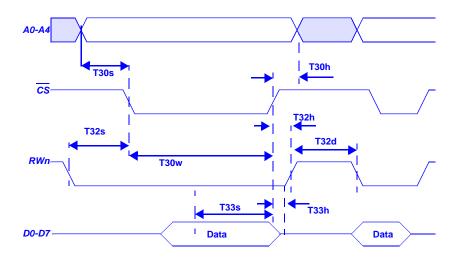

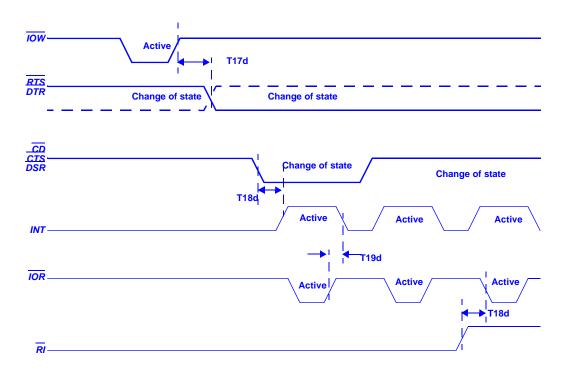

The intel bus interface mode is enabled by connecting  $16/\overline{68}$  pin to high. This enables the IMP16C654 to interface easily with the intel processor bus interface. Each UART is selected with its individual chip select (CSA, CSB, CSC, CSD) pins. When selected, the UARTs respond according to the state of IOW and IOR signals.

#### The Motorola Bus Interface Mode

The motorola bus interface mode is enabled by connected the  $16/\overline{68}$  pin to a logic low. In this mode, the individual UARTs are selected by a common select input and the address inputs A3,A4 according to the table shown below. The RWn input determines if the current bus cycle is read or write.

| CS | A4 | A3 | UART Channel |

|----|----|----|--------------|

| 1  | X  | Х  | None         |

| 0  | 0  | 0  | А            |

| 0  | 0  | 1  | В            |

| 0  | 1  | 0  | С            |

| 0  | 1  | 1  | D            |

Table 2 : UART Channel Selection, Motorola Mode Interface

#### **Internal Registers**

The IMP16C654 provides 16 internal registers per channel for monitoring and control of UART channels. These resisters are shown in Table below. These registers are similar to those already available in the standard 16C554/16C454. These registers function as data holding registers (THR/RHR), interrupt status and control registers (IER/ISR), FIFO control register(FCR), line status and control registers (LCR/LSR), modem status and control registers (MCR/MSR), programmable baud rate registers (DLL/DLM), and a general purpose scratch pad register (SPR). Additional registers include enhanced features registers EFR, Flow control character registers. The following table shows the register map. Refer to register description section for further details on individual registers.

## **Data Communications**

#### Table 3 : Internal Register

| A2            | A1              | A0              | Read Mode                               | Write Mode                |

|---------------|-----------------|-----------------|-----------------------------------------|---------------------------|

| General Regi  | sters accessibl | e only when LC  | R is not 0xBF                           |                           |

| 0             | 0               | 0               | Receive Holding Register                | Transmit Holding Register |

| 0             | 0               | 1               | Interrupt Enable Register               | Interrupt Enable Register |

| 0             | 1               | 0               | Interrupt Status Register               | FIFO Control Register     |

| 0             | 1               | 1               | Line Control Register                   | Line Control Register     |

| 1             | 0               | 0               | Modem Control Register                  | Modem Control Register    |

| 1             | 0               | 1               | Line Status Register                    | Factory Test Register     |

| 1             | 1               | 0               | Modem Status Register                   | NA                        |

| 1             | 1               | 1               | Scratch Pad Register                    | Scratch Pad Register      |

| Baud Rate Re  | egister Set (DL | L/DLM) accessi  | ble when LCR[7] = 1 and LCR is not 0xBF |                           |

| 0             | 0               | 0               | LSB of Divisor Latch                    | LSB of Divisor Latch      |

| 0             | 0               | 1               | MSB of Divisor Latch                    | MSB of Divisor Latch      |

| Enhanced Re   | gister accessib | ble only when L | CR is 0xBF                              |                           |

| 0             | 1               | 0               | Enhanced Feature Register               | Enhanced Feature Register |

| 1             | 0               | 0               | Xon-1 Byte                              | Xon-1 Byte                |

| 1             | 0               | 1               | Xon-2 Byte                              | Xon-2 Byte                |

| 1             | 1               | 0               | Xoff-1 Byte                             | Xoff-1 Byte               |

| 1             | 1               | 1               | Xoff-2 Byte                             | Xoff-2 Byte               |

| FIFO Status F | Register (Acces | ssed when FSR   | S is active.)                           |                           |

| x             | x               | x               | FSR                                     | NA                        |

#### **Flow Control**

The IMP16C654 allows both in-band and out-of-band flow control. This is explained in detail in the text below.

#### In-band Flow Control

The IMP16C654 can control the flow of data on the serial interface using the TX/RX lines. When enabled, the receiver compares one or two sequential characters received with the programmed Xon/Xoff characters. If a match is found to the programmed Xoff characters, the transmitter will pause data transmission as soon as the current character is completely transmitted. The receiver continues to monitor the Rx input and when a match is found to the programmed Xon characters, the transmitter will resume the transmit operation starting from the next data byte in the FIFO. The happening of these events can also be indi-

cated to the application by generating an interrupt if programmed to do so. Both the Xon/ Xoff characters are user programmable.

A special Xon mode is also available in IMP16C654. Subsequent to pausing transmission because of xoff character reception, the transmitter can resume transmission as soon as the receiver receives any character.

Similarly while receiving data, if in-band flow control is enabled, an xoff character is sent by the transmitter when the receive fifo contains the programmed trigger level to indicate to the remote device to pause transmission. When the receive fifo level falls below the trigger level, the transmitter transmits Xon character/s to indicate to the remote device to resume transmission. Various options available for in-band flow control are described in the EFR register description. The IMP16C654 also provides a mode in which the received XOFF/XON characters are transfers to receive FIFO like any other character.

While comparing the incoming characters with the programmed XON/XOFF characters, only the programmed number of bits per character are compared. This is controlled by LCR bits 0-1.

#### **Out-Of-Band Flow Control**

The IMP16C654 can be programmed to achieve data flow control using RTS/CTS signals. In this case, the RTS output pin is used to request remote unit to pause/resume transmission while the CTS input pin is monitored to control the local transmission. When the data in the receive FIFO exceeds the programmed trigger level, the RTS pin is deasserted. This is connected to remote CTS pin which indicates to the remote transmitter to stop transmission. When the data in receive fifo falls below the trigger level, the RTS pin is reasserted and the remote transmitter resumes transmission. The local transmitter stops transmission when the local CTS input is deasserted after completing the current character transmission. It resumes transmission when the CTS pin reasserts. Interrupts can be generation on a change of state on the CTS/RTS pins to inform the application about the status of the transmitter/receiver.

In order to increase the through put, the IMP16C654 provides RTS hysteresis using the trigger levels. This reduces the RTS switching and provides more effective flow control.

#### Interrupts

The device contains 128 deep byte wide transmit fifo and 128 deep 11 bit wide receive fifo. The receive fifo also stores the error conditions. The IMP16C654 includes programmable trigger levels for the transmit fifo also and the interrupt can be generated according to these programmed trigger levels. Same is true with the receive fifo.

In addition, the receive fifo has a logic that generates time-out interrupt if the receive FIFO contains data but the number of bytes is less than the programmed trigger level and there is no activity at the FIFO input/output for 4 consecutive character time. This enables the application the handle the end of a receive packet successfully without any latency in receiving a complete packet or loosing received data.

Each UART provides seven interrupts. The transmit holding interrupts is generated whenever the transmit FIFO is empty if the interrupt is enabled. This interrupt is disabled when the interrupt status register is read or transmit FIFO is loaded with new data. The receive data interrupt is generated when the receive fifo level reaches the programmed trigger level. The receiver also provide the time-out interrupt which has been described above. In

## **Data Communications**

addition it also provides the line status interrupt cause by an error condition being observed in the receiver which can be because of parity incorrectness, framing incorrectness, overrun or break detection on the Rx input. Any change in modem status inputs can also cause an interrupts to be generated. Other two interrupts can be generated by the auto flow control is enabled and an flow control option is exercised during transmission or reception of data. Each of the interrupt conditions mentioned above are individually maskable.

The interrupt outputs can be controlled according to system requirements. The system/ board designer can optionally use software controlled three state interrupt operation. This is accomplished by INTSEL and MCR bit-3. When INTSEL interface pin is left open or made a logic 0, MCR bit-3 controls the three state interrupt outputs, INT A-D. When INT-SEL is a logic 1, MCR bit-3 has no effect on the INT A-D outputs and the package operates with interrupt outputs enabled continuously.

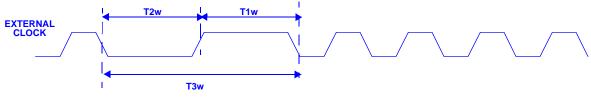

#### **Programmable Baud Rate Generator**

Single baud rate generator per UART channel is provided for the transmitter and receiver, allowing independent TX/RX channel control. The programmable Baud Rate Generator can work with an input clock up to 24 MHz. It can be configured for internal or external clock operation. For internal clock oscillator operation, an industry standard microprocessor crystal (parallel resonant/ 22-33 pF load) is connected externally between the XTAL1 and XTAL2 pins (see figure 8). Alternatively, an external clock can be connected to the XTAL1 pin to clock the internal baud rate generator for standard or custom rates.

The generator divides the input 16X clock by any divisor from 1 to 2<sup>16</sup>-1. The device divides the basic crystal or external clock by 16. Further division of this 16X clock provides two table rates to support low and high data rate applications using the same system design. Customized Baud Rates can be achieved by selecting the proper divisor values for the MSB and LSB sections of baud rate generator. Using the CLKSEL input, a prescaler that divides the input clock by 4 or 1 can be selected to achieve wide range of baud rates.

Programming the Baud Rate Generator Registers DLM (MSB) and DLL (LSB) provides a user capability for selecting the desired final baud rate. The example in Table below, shows the two selectable baud rate tables available when using a 7.3728 MHz crystal.

Figure 8: Crystal oscillator connection

| Output Baud Rate<br>(1.8432 MHz<br>Clock) | Output Baud Rate<br>(7.3728 MHz<br>Clock) | User 16 x Clock<br>Divisor (Decimal) | User 16 x Clock<br>Divisor (HEX) | DLM Program<br>Value (HEX) | DLL Program<br>Value (HEX) |

|-------------------------------------------|-------------------------------------------|--------------------------------------|----------------------------------|----------------------------|----------------------------|

| 50                                        | 200                                       | 2304                                 | 900                              | 09                         | 00                         |

| 300                                       | 1200                                      | 384                                  | 180                              | 01                         | 80                         |

| 600                                       | 2400                                      | 192                                  | C0                               | 00                         | C0                         |

| 1200                                      | 4800                                      | 96                                   | 60                               | 00                         | 60                         |

| 2400                                      | 9600                                      | 48                                   | 30                               | 00                         | 30                         |

| 4800                                      | 19.2K                                     | 24                                   | 18                               | 00                         | 18                         |

| 9600                                      | 38.4K                                     | 12                                   | 0C                               | 00                         | 0C                         |

| 19.2K                                     | 76.8K                                     | 6                                    | 06                               | 00                         | 06                         |

| 38.4K                                     | 153.6K                                    | 3                                    | 03                               | 00                         | 03                         |

| 57.6K                                     | 230.4K                                    | 2                                    | 02                               | 00                         | 02                         |

| 115.2K                                    | 460.8K                                    | 1                                    | 01                               | 00                         | 01                         |

#### Table 4 : DLL / DLM values for different Baud Rates

#### **DMA Operation**

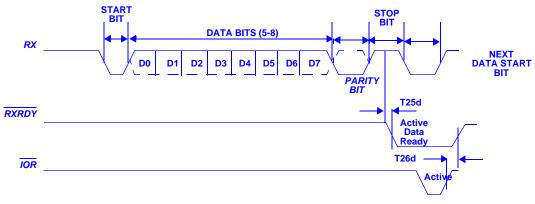

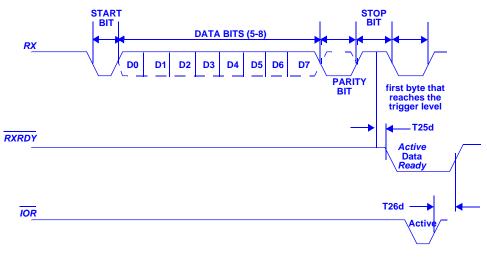

The IMP16C654s deeper FIFO levels allow effective use of the DMA for block transfer of data to/from UART. When the FIFO is enabled and the DMA mode is also enabled, the application can use the RXRDY and TXRDY to transfer block data from /to the individual uart. When DMA mode is enabled, the RXRDY goes low when the programmed receiver trigger level is reached or a receive time-out has occurred. Once activated, the RXRDY will go high only when there are no more characters in the receive FIFO. This facilitates the use of RXRDY for DMA block transfer of data from the UART to the system memory. Similarly when DMA mode is enabled, the TXRDY goes low when at least 1 byte in the FIFO is empty and goes high when the FIFO is full. This facilitates the use of TXRDY output for DMA block transfers of data to the transmit FIFO.

#### Low Power Mode

The IMP6C654 allows the control of low power mode for the device by the software. If enabled by a write to IER, the device goes into low power mode. The device will not go into lowe power mode if any interrupt causing condition is active. The device automatically wake up when it detects the start bit or a change of state on modem status inputs or transmit data provided by the application. The device will return to low power mode of operation when the last data byte is read from the receive fifo or the last data byte for transmit has been transmitted.

#### Loopback Mode

## **Data Communications**

The internal loopback capability allows onboard diagnostics. In the loopback mode the normal modem interface pins are disconnected and reconfigure for loopback internally. MCR register bits 0-3 are used for controlling loopback diagnostic testing. In the loopback mode OP1 and OP2 in the MCR register (bits 3/2) control the modem RI and CD inputs respectively. MCR signals DTR and RTS (bits 0-1) are used to control the modem CTS and DSR inputs respectively. The transmitter output (TX) and the receiver input (RX) are disconnected from their associated interface pins, and instead are connected together internally. The CTS, DSR, CD, and RI are disconnected from their normal modem control input pins, and instead are connected internally to DTR, RTS, OP1 and OP2. Loopback test data is entered into the transmit holding register via the user data bus interface, D0-D7. The transmit UART serializes the data and passes the serial data to the receive UART via the internal loopback connection. The receive UART converts the serial data back into parallel data that is then made available at the user data interface, D0-D7. The user optionally compares the received data to the initial transmitted data for verifying error free operation of the UART TX/RX circuits.

## **Register** Description

The following description provide details of the different registers in the IMP16C654, the bits in the registers and their functionality.

#### THR - Transmit Holding Register

Register address: 3'b000. Post Reset Condition: 0xXX. Register Access Condition: LCR[7] = 0.

| Bit | Signal             | R/W | Description                                                                                                                                                                                                                                                                                                                                                                                   |

|-----|--------------------|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:0 | Transmit Data Byte | W   | The register holds the transmit data prior to transmission. The status of this register is reflected in the LSR bit 5. Writing to the THR transfers the contents of the data bus (D7-D0) to the THR. If FIFO is enabled, a write to this location transfers the data to the fifo. A write to the register should not be attempted when the LSR bit 5 is low, indicating the THR/FIFO is full. |

#### Table 5 : Transmit Holding Register Bits

**RHR - Receive Holding Register** Register address: 3'b000. Post Reset Condition: 0xXX. Register Access Condition: LCR[7] = 0.

## **Data Communications**

.

#### Table 6 : Receive Holding Register Bits

| Bit | Signal             | R/W | Description                                                                                                                            |

|-----|--------------------|-----|----------------------------------------------------------------------------------------------------------------------------------------|

| 7:0 | Received Data Byte | R   | The register holds the received data prior to application reading the byte. The status of this register is reflected in the LSR bit 0. |

Register Name: **IER - Interrupt Enable Register** Register address: 3'b001. Post Reset Condition: 0x00. Register Access Condition: LCR[7] = 0.

| D:4 | Cinnel                          | DAK | Description                                                                                                                                                                                                                                                                                                                                                 |

|-----|---------------------------------|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Bit | Signal                          | R/W | Description                                                                                                                                                                                                                                                                                                                                                 |

| 0   | RHR Interrupt Enable            | RW  | This bit when high enables a received byte to generate a inter-<br>rupt to the application when FIFO is not enabled. When FIFO is<br>enabled and it reaches the trigger level, and interrupt is gener-<br>ated if this bit is set.                                                                                                                          |

| 1   | THR Interrupt Enable            | RW  | This bit when set and the transmit FIFO level falls below the pro-<br>grammed trigger level, a interrupt is generated for the applica-<br>tion. If FIFO is not enabled, the THR empty condition will<br>generate and interrupt for the application.                                                                                                         |

| 2   | Rx Line Status Interrupt Enable | RW  | This bit when set enables any receive error condition to gener-<br>ate an interrupt for the application. These errors can be framing<br>error, parity error, overrun error or break error.                                                                                                                                                                  |

| 3   | Modem Status Interrupt Enable   | RW  | This bit when set enables a change in modem status inputs to generate an interrupt for the application.                                                                                                                                                                                                                                                     |

| 4   | Sleep Mode Enable               | RW  | Can be read/written only if EFR[4] = 1. When set, it enables the device to go into sleep mode. The device cannot go into sleep mode if any interrupt conditions are pending. The device awakes from sleep mode when it detects data write to the transmit holding register or receiver detects a start bit or any of the modem status inputs changes state. |

| 5   | Xoff Interrupt Enable           | RW  | Can be read/written only if $EFR[4] = 1$ . When set, it enables the device to generate an interrupt when the receiver receives an Xoff byte.                                                                                                                                                                                                                |

| 6   | RTS Output Interrupt Enable     | RW  | Can be read/written only if EFR[4] = 1. Enables generation of an interrupt when RTS pin transitions from logic 0 to logic1 when set.                                                                                                                                                                                                                        |

| 7   | CTS Input Interrupt Enable      | RW  | Can be read/written only if EFR[4] = 1. Enables generation of an interrupt when CTS pin transitions from logic 0 to logic1 when set.                                                                                                                                                                                                                        |

#### Table 7 : Interrupt Enable Register Bits

Register Name: **FCR -FIFO Control Register** Register address: 3'b010. Post Reset Condition: 0x00. Register Access Condition: LCR != 0xBF.

| Table 8 : | FIFO Cor | ntrol Regis | ster Bits |   |

|-----------|----------|-------------|-----------|---|

|           |          |             |           | _ |

| Bit | Signal            | R/W | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|-----|-------------------|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0   | FIFO Enable       | W   | This bit when high enables the fifos for receive and transmit data. When low, it disables the FIFO. Note that the bit must be high when any access to the other FCR bits is made.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 1   | RX Fifo Reset     | W   | This bit when set clears the receive fifo. The character in the receive shift register is not cleared. This is a auto clear bit and is cleared by the device when the Rx FIFO is cleared.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 2   | Tx Fifo Reset     | W   | This bit when set clears the transmit fifo. The character in the transmit shift register is not cleared. This is a auto clear bit and is cleared by the device when the Tx FIFO is cleared.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 3   | DMA Mode Select   | W   | This bit selects the DMA mode. This bit controls the operation of TXRDY and RXRDY pins.<br>When this bit is low, the TXRDY goes low when there are no characters in the THR/TxFIFO and goes high when at least one byte is loaded into the THR/TxFIFO. The RXRDY goes low when there is at least 1 byte in the RxFifo/RHR. It will go high when there are no more bytes in the RHR/RxFIFO.<br>When this bit is high, the TXRDY goes low when the THR/TxFIFO has at least one byte empty and goes high when the TXFIFO has at least one byte empty and goes high when the TXFIFO is full. The RXRDY goes low when the programmed trigger level is reaches or receive time-out occurs and goes high when there are no more characters in the receive FIFO. |

| 4-5 | Tx Trigger Select | W   | These bits are used to select appropriate trigger level for the transmit FIFO. For detailed information, refer to the text below this table.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 7-6 | Rx Trigger Select | W   | These bits are used to select appropriate trigger level for the receive FIFO. For detailed information, refer to the text below this table.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

#### FCR BIT 4-5:

The FCTR bits 4-5 are associated with these two bits and select one of the 4 tables given below for the transmit trigger level. The IMP16C654 will issue a transmit empty interrupt when the number of characters in the FIFO falls below the selected trigger level.

| Table 9 : Transmit Trigger | Level Selection Details |

|----------------------------|-------------------------|

|----------------------------|-------------------------|

| FCR[5:4] | Mode |

|----------|------|

| 00       | 8    |

#### Table 9 : Transmit Trigger Level Selection Details

| FCR[5:4] | Mode |

|----------|------|

| 01       | 16   |

| 10       | 32   |

| 11       | 56   |

FCR BIT 6-7: (logic 0 or cleared is the default condition, Rx trigger level = 1)

These bits are used to set the trigger level for the receive FIFO interrupt.

An interrupt is generated when the number of characters in the FIFO equals the programmed trigger level. However the FIFO will continue to be loaded until it is full.

| FCR[7:6] | Mode |

|----------|------|

| 00       | 8    |

| 01       | 16   |

| 10       | 56   |

| 11       | 60   |

#### Table 10 : Receive Trigger Level Selection Details

Register Name: **ISR Interrupt Status Register** Register address: 3'b010. Post Reset Condition: 0x01. Register Access Condition: LCR != 0xBF.

| Bit | Signal                    | R/W | Description                                                                                                                                                                            |

|-----|---------------------------|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0   | Interrupt Status          | R   | This bit when high indicates that no interrupt is pending the UART. When low, bits 5-1 indicate the cause of highest priority interrupt pending. For details refer to the table below. |

| 5-1 | Highest Interrupt pending | R   | When the bit 0 is low, these bits point to the highest priority inter-<br>rupt pending service in the UART. For details refer to table<br>below.                                       |

| 7-6 | FIFO Enable Status        | R   | These bits are 2'b11 when the FIFO in the UART are enabled.<br>When these bits are read as 2'b00, the UART fifo's are not<br>enabled.                                                  |

#### Table 11 : Interrupt Status Register Bits

.

ISO 9001 Registered

| Priority |       |       | [ISR  | BITS] |       |       | Source Of The Interrupt                         | Interrupt clearing                                                                                      |  |

|----------|-------|-------|-------|-------|-------|-------|-------------------------------------------------|---------------------------------------------------------------------------------------------------------|--|

| Level    | BIT-5 | BIT-4 | BIT-3 | BIT-2 | BIT-1 | BIT-0 |                                                 |                                                                                                         |  |

| 1        | 0     | 0     | 0     | 1     | 1     | 0     | LSR (Receiver Line Status Regis-<br>ter)        | Read of LSR/ Read of RHR                                                                                |  |

| 2        | 0     | 0     | 0     | 1     | 0     | 0     | RXRDY (Received Data Ready)                     | Read of RHR                                                                                             |  |

| 2        | 0     | 0     | 1     | 1     | 0     | 0     | RXRDY (Receive Data Time Out)                   | Read of RHR                                                                                             |  |

| 3        | 0     | 0     | 0     | 0     | 1     | 0     | TXRDY (Transmitter Holding Regis-<br>ter Empty) | Read of ISR/Write to THR                                                                                |  |

| 4        | 0     | 0     | 0     | 0     | 0     | 0     | MSR (Modern Status Register)                    | Read of MSR                                                                                             |  |

| 5        | 0     | 1     | 0     | 0     | 0     | 0     | Received Xoff/Special character.                | Read of ISR. Read of ISR for<br>special charagter interrupt,<br>reception of Xon for Xoff<br>interrupt. |  |

| 6        | 1     | 0     | 0     | 0     | 0     | 0     | CTS/RTS change of state interrupt.              | Reset of MSR                                                                                            |  |

#### Table 12 : Interrupt Source Table

Register Name: LCR **-Line Control Register** Register address: 3'b011. Post Reset Condition: 0x00. Register Access Condition: Always Accessible.

| Bit | Signal           | R/W | Description                                                                                                                                                                                                                                                                                                                                                                           |

|-----|------------------|-----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1-0 | Character Length | RW  | These bits select the bits / character to be transmitted/received.<br>When 00, 5 bits are transmitted and received per character,<br>when 01, 6 bits, when 10, 7 bits and when 11 8 bits are transmit-<br>ter/received per character.                                                                                                                                                 |

| 2   | Stop Bits        | RW  | When 0, one stop bit is transmitter per character.<br>When this bit is set and 5 bits per character is selected as char-<br>acter length, 1.5 stop bits are transmitted per character. When<br>set and any other character length is selected, two stop bits are<br>transmitter per character. Please note that the receiver looks for<br>only one stop bit irrespective of this bit. |

| 3   | Parity Enable    | RW  | When 0, no parity bit is transmitted or expected by the receiver<br>in the character. When high, a parity bit is transmitted and the<br>receiver expects a parity bit in the character frame.                                                                                                                                                                                         |

## **Data Communications**

| Bit | Signal                          | R/W | Description                                                                                                                                                                                                         |

|-----|---------------------------------|-----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 4   | Parity Select                   | RW  | When parity is enabled, this bit when high selects even parity<br>and when low selects odd parity for transmission and reception.<br>For selecting even/odd parity, "Force parity" bit must be 0.                   |

| 5   | Force Parity                    | RW  | When parity is enabled, and this bit is set, parity bit is forced to 1 if "parity select" is set to 0 and parity bit is forced to 0 if "parity select" is set to 1.                                                 |

| 6   | Transmit Break Enable           | RW  | When set, the transmitter forces the TX output to logic 0. When cleared, the transmitter starts sending the data from the shift register.                                                                           |

| 7   | DLAB - Divisor Latch Access Bit | RW  | When set, enables the baud rate divisor latches to be accessible<br>for programming. When 0, divisor latches are not accessible and<br>THR/RHR and IER register are accessible at the divisor latches<br>addresses. |

#### Table 13 : Line control Register Bits

Register Name: MCR **-Modem Control Register** Register address: 3'b100. Post Reset Condition: 0x00. Register Access Condition: LCR != 0xBF.

#### Table 14 : Modem Control Register Bits

| Bit | Signal         | R/W | Description                                                                                                                                                                                                             |

|-----|----------------|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0   | DTR Control    | RW  | When cleared, forces the DTR pin to go high. When set, DTR output is forced low.                                                                                                                                        |

| 1   | RTS Control    | RW  | When cleared, forces the RTS pin to go high. When set, RTS output is forced low.                                                                                                                                        |

| 2   | OP1 Control    | RW  | Bit is used in loopback mode only. This bit is used to control the state of RI interface signal in loopback mode.                                                                                                       |

| 3   | OP2 Control    | RW  | When cleared, it forces the INTA-D outputs to tristate operation<br>in intel mode. When set, it forces INTA-D into continuous opera-<br>tion in intel mode. In loopback mode, it is used to control the<br>state of CD. |